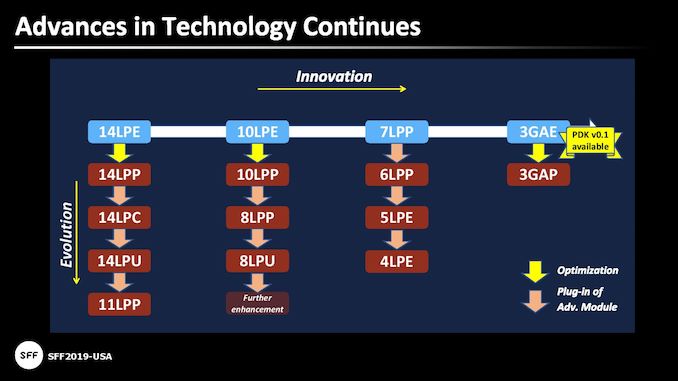

بعد از 7 نانومتر، 6 نانومتر، 5 نانومتر و 4 نانومتر چه می آید؟ درست است، 3 نانومتر! در رویداد Foundry Forum سامسونگ ، سامسونگ اعلام کرد که اولین نسخه آلفای کیت طراحی محصول برای اولین فرآیند 3 نانومتری اش اکنون برای مشتریان آماده است. آنچه این خبر را ویژه می کند این است که 3 نانومتر نقطه تلاقی جایی است که سامسونگ قصد دارد نسل بعدی فناوری (Gate-All-Around (GAA را که جایگزین FinFET می شود ، معرفی کند.

فراتر از FinFET: حرکت به سوی Gate-All-Around

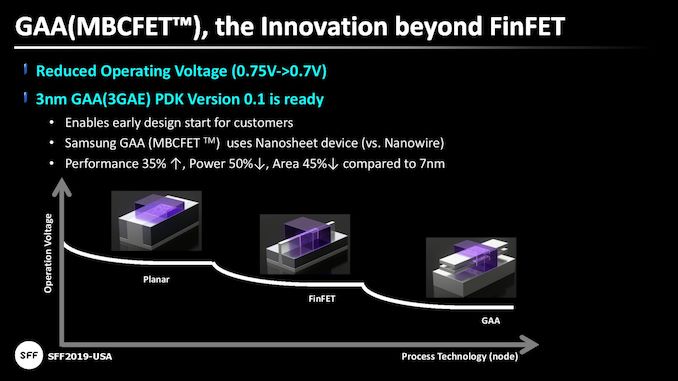

عامل اصلی نوآوری در فن آوری های فرآیند مبتنی بر منطق طی دهه گذشته FinFET بوده است. در مقایسه با ترانزیستور مسطح استاندارد ، با کاهش گره فرآیند ، FinFET امکان عملکرد و مقیاس گذاری ولتاژ بهتر را فراهم می کند و جنبه های منفی محدودیت های ترانزیستور را به حداقل می رساند. FinFET ها با افزایش سطح تماس بین کانال ترانزیستور و گیت با مقیاس گذاری در جهت عمودی کار می کنند ، که باعث می شود زمان تعویض سریع تر و تراکم جریان بالاتر در مقایسه با یک طرح مسطح باشد.

با این حال ، مانند ترانزیستورهای مسطح ، ترانزیستورهای FinFET در نهایت به نقطه ای می رسند که با کوچک شدن گره های فرآیند ، نمی توانند مقیاس بندی کنند. برای مقیاس گذاری ، منطقه تماس بین کانال و گیت باید افزایش یابد و روش انجام این کار استفاده از طرح Gate-All-Around (GAA) است. GAA ابعاد ترانزیستور را تنظیم می کند تا اطمینان حاصل کند که گیت زیر کانال نیز هست ، نه تنها در بالا و طرفین. این اجازه می دهد تا طراحی GAA ترانزیستورها را بجای جانبی به صورت عمودی روی هم قرار دهد.

FET های مبتنی بر GAA (GAAFET) می توانند از فاکتورهای مختلفی برخوردار باشند. بیشتر تحقیقات به GAAFET مبتنی بر نانوسیم اشاره دارد که دارای عرض کانال کم است و کانال را تا حد ممکن کوچک می کند. این نوع GAAFET معمولاً برای طراحی کم مصرف مفید است ، اما ساخت آن دشوار است. نوع دیگر ، ایجاد کانال مانند یک صفحه افقی و افزایش حجم کانال است که از مزایای عملکرد و مقیاس گذاری برخوردار است. این GAAFET مبتنی بر ورق نانو همان چیزی است که سامسونگ از آن به عنوان کانال چند پل FET یا MBCFET نام می برد که قرار است به عنوان یک مارک تجاری برای این شرکت باشد.

در جایی که ترانزیستورهای مسطح حدود 22 نانومتر / 16 نانومتر باشند ، با پایین آمدن از 22 نانومتر / 14 نانومتر به 5 نانومتر و 4 نانومتر ، FinFET ایده آل بوده است. سامسونگ قصد دارد GAAFET های مبتنی بر ورق نانو را در طرح 3 نانومتری خود معرفی کند تا به طور کامل جایگزین FinFET شوند.

Building on 3nm: PDKs

هنگامی که یک شرکت نیمه هادی تراشه جدیدی را در یک فرآیند مشخص طراحی می کند ، یکی از ابزارهای مورد نیاز آنها کیت طراحی از ریخته گری که قصد استفاده از آن را دارد، است. به عنوان مثال هر کسی که امروزه معماری Arm روی تراشه 14 نانومتری ایجاد می کند ، Arm را فراخوانی می کند و کیت طراحی Cortex-A55 را برای سامسونگ یا TSMC یا GlobalFoundries درخواست می کند ، که برای این فرآیند بهینه شده است. برای 14 نانومتر ، این کیت های طراحی بسیار بالغ هستند و بسته به اینکه بخواهید فرکانس بالا داشته باشید یا بهینه سازی انرژی کم ، Arm احتمالاً نسخه های مختلفی را ارائه می دهد.

با این وجود وقتی فناوری فرآیند جدید است ، نسخه های اولیه آلفا و بتا این کیت های طراحی محصول (PDK ها) در دسترس قرار می گیرند. PDK حاوی قوانین طراحی فرآیند و همچنین بهینه سازی هایی است که برای ایجاد بهترین نتیجه برای قدرت و عملکرد به کار می رود. به طور معمول ، ریخته گری با تولید تراشه های بیشتر و آزمایش تغییرات بیشتر ، PDK را به روز می کند تا به مشتریان خود کمک کند بهترین تراشه ها را تولید کنند.

Nuance با MBCFET

یکی از ویژگی های MCBFET که به طور خاص در بیانیه مطبوعاتی سامسونگ ذکر نشده است این است که FET های مبتنی بر ورق نانو بسیار قابل تنظیم هستند. عرض صفحه نانو یک معیار اصلی در تعریف قدرت و ویژگی های عملکرد است: هرچه عرض بیشتر باشد ، عملکرد (در توان بالاتر) نیز بهتر است. سامسونگ برای ایجاد بهینه سازی همزمان در همان طراحی تراشه ، چهار پهنای مختلف ورق نانو را در PDK خود گنجانده است: طرح های ترانزیستوری که روی توان کم تمرکز دارند می توانند از صفحات نانو کوچکتر استفاده کنند ، در حالی که منطقی که به عملکرد بالاتر نیاز دارد ، می تواند برای ورق های گسترده تر باشد ولی در نهایت این یک مقیاس مداوم است. در مقابل ، FinFET ها فقط یک نقطه طراحی توان / فرکانس در یک طراحی گره فرایند برای تعداد پره داده شده دارند ، و فقط پروفایل های گسسته را ایجاد می کنند.

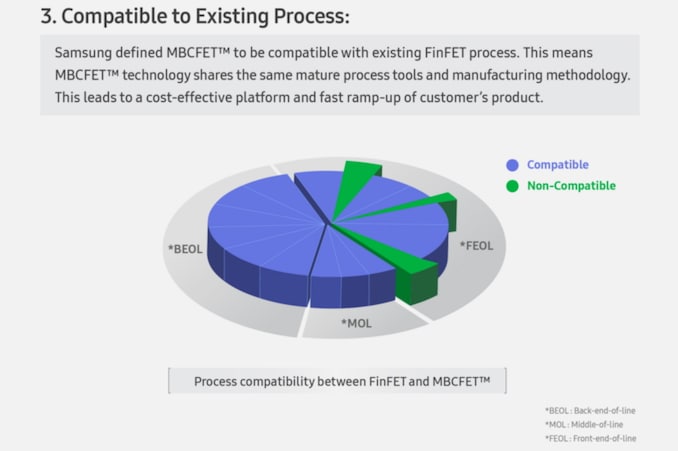

سامسونگ اظهار داشت که طراحی 3GAE بدون در نظر گرفتن طرح عرض ورق مورد نیاز ، امکان انتقال مستقیم IP از هر 4 طرح خانواده 4nm را فراهم می کند. 3GAE و 4LPP همان قوانین طراحی BEOL را دارند که این امکان را فراهم می کند.

تحقیقات TSMC در مورد مواد در ابعاد پایین همچنین شامل بررسی نانولوله های کربنی یک بعدی است. یک مشکل اساسی در کانالهای ترانزیستوری با استفاده از نانولوله های کربنی ، نیاز به تولید ماده دی الکتریک گیت است که به ما اجازه استفاده از ترانزیستورهایی با طول گیت کوتاه می دهد. به گفته دکتر لیو ، تحقیقات نشان داده است که اکنون این امکان وجود دارد ، با داشتن ماده ای (که در بالا نشان داده شده است) که توانایی یک high-k gate stack مناسب برای ساخت ترانزیستور هایی با عرض گیت 10 نانومتر را داشته باشد.

سامسونگ GAA MBCFET PDK سه نانویی ، ورژن 0.1 را معرفی می کند

اعلامیه امروز این است که سامسونگ اولین نسخه آلفای PDK را برای فرآیند تولید 3 نانومتری نسل اول خود که از MBCFET استفاده می کند ، ارائه می دهد. سامسونگ این فرآیند را فرآیند ‘3GAE’ خود می نامد و با این نسخه آلفا به شرکای خود اجازه می دهد تا با برخی از قوانین طراحی جدید برای روند 3GAE آشنا شده و با چالش های آن گلاویز شوند.

سامسونگ با اولین روند 3GAE وعده های زیادی داده است. یکی از عناوین اصلی کاهش ولتاژ کار از 0.75 ولت به 0.70 ولت است که گام خوبی در قدرت خواهد بود. مقادیر عنوان PPA که سامسونگ اعلام کرده نیز چشمگیر است: در مقایسه با 7 نانومتر ، 3GAE عملکرد 1.35 برابر ، قدرت 0.5 برابر و با سطح قالب 0.65 برابر ارائه می دهد.

سامسونگ اظهار داشت که این اعداد عملکردی براساس استفاده از سلولهای با عرض بزرگتر برای مسیرهای مهم که فرکانس در آنها مهم است و سلولهای با عرض کمتر برای مسیرهای غیر بحرانی که صرفه جویی در مصرف انرژی در آنها بسیار مهم است ، انجام می شود. از نظر فنی Fmax وسیعترین سلولها 1.5x ذکر شده است ، در حالیکه توان Fmax 0.6x است. توان در iso-performance همان جایی است که عدد 0.5x از آنجا می آید.

برای بیان برخی از این موارد ، سامسونگ انتظار دارد که روند 3GAE خود اولین تولیدعمده ی مشتری را در سال 2020 با risk production در اواخر سال 2020 و volume manufacturing در اواخر سال 2021 ارائه دهد.

فراتر از 3GAE ، سامسونگ قبلاً توضیح داده است که فرایند 3 نانومتری نسل دوم آن 3GAP نامیده می شود ، با تمرکز بر عملکرد با کارایی بالا. روند 3GAP با بهره گیری از آنچه سامسونگ از 3GAE آموخته است ، بهینه سازی متمرکز خواهد شد. 3GAE با تولید انبوه در سال 2022 در معرض risk production قرار خواهد گرفت.

ابزارهای PDK و شرکای (partners) EDA

برای علاقه مندان ، ابزار PDK شامل SPICE ، DRC ، LVS ، PEX ، P-Cell ، Fill Deck و P&R Techfile است. شرکای EDA شامل Cadence ، Mentor و Synopsys هستند.

خبرهای مرتبط

ارتقای عظیم زیرسیستم ویندوز برای کاربران لینوکس

CPU Thread چیست؟

CPU به عنوان مغز دستگاه محاسباتی….

پاسخ اینتل به اپل بعد از مدت ها چشم انتظاری

کامپیوتر های کوانتومی محاسبات مشترک را میاموزند..

Severin Daiss و Stefan Langenfeld وهمکارانشون….