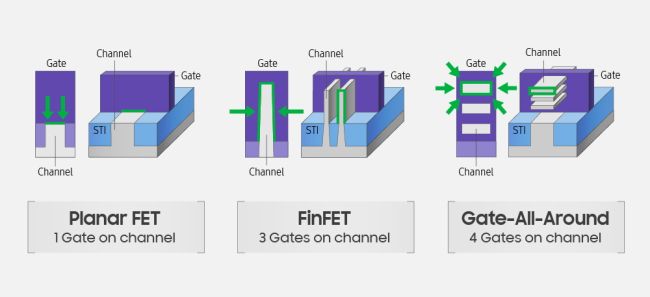

یک طرح ترانزیستور جایگزین احتمالی برای finFET ها.

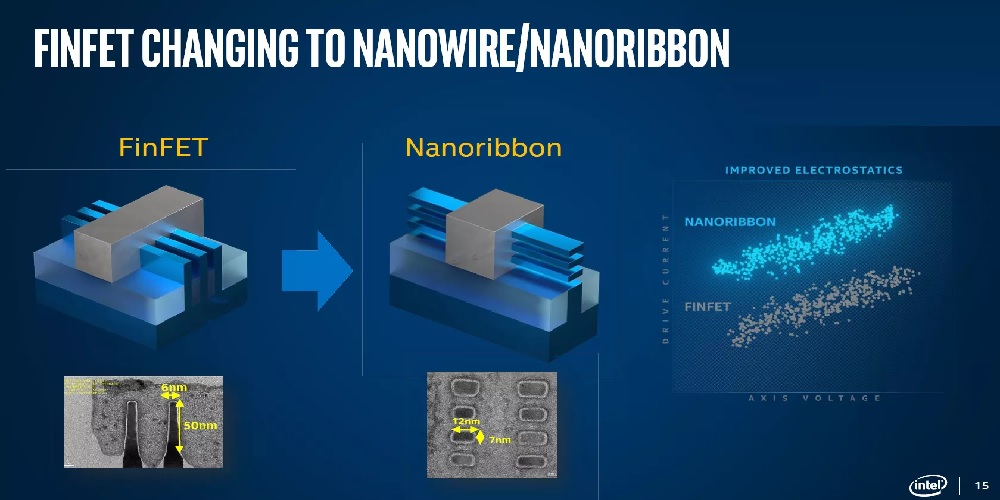

همانطور که عرض fin در یک finFET به 5 نانومترنزدیک می شود ، تغییرات عرض کانال می تواند باعث تغییرپذیری نامطلوب و از دست دادن قابلیت تحرک(موبیلیته) شود. یک ترانزیستور کاندید آینده دار و آینده نگر – GAAFET – می تواند این مشکل را حل کند.در GAAFET ها گیت در چهار طرف آن قرار میگرد و آن را احاطه میکند در واقع جنس آنها ار نانوسیم های سیلیکونی هستند که یک گیت دور آنها را فراگرفته اس.ت.بعضی مواقع این جنس میتواند تغییر کند و از ایندیم گالیم آرسناید(InGaAs) یا سایر مواد گروه III-V تشکیل شود.

ورق های نانوGAAترانزیستور (Nanosheet GAA)

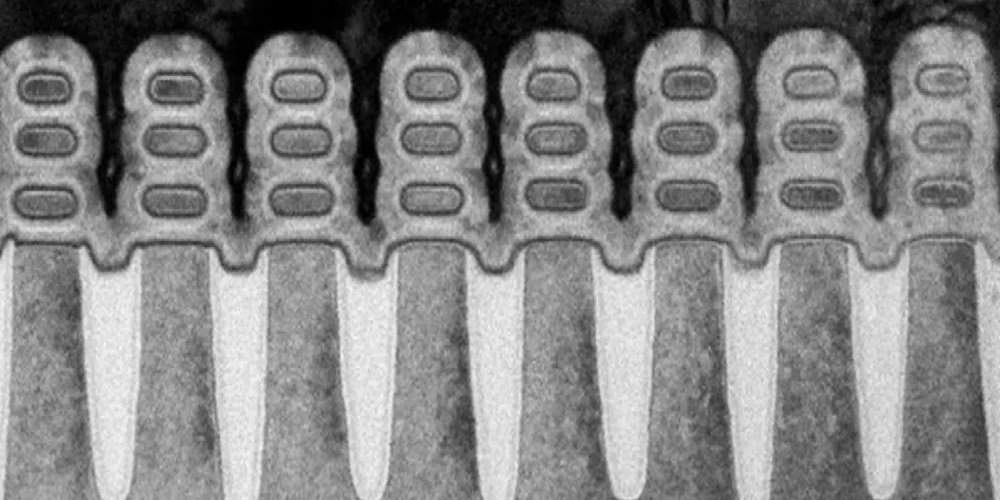

طبق گفته ی شرکت IBM نانو ورق های انباشته شده به صورت افقی به عنوان اجماع صنعت برای 5 نانومتر در حال ظهور هستند. این دستگاه ها با لایه های متناوب سیلیکون و سیلیکون ژرمانیم (SiGe) شروع می شوند که به شکل ستونهایی در آمده اند.

ساخت ساختار نا همگون اولیه ی Si/SiGe سرراست است و الگوی ستون مشابه ساختار fin است. با این حال چند قدم بعدی منحصر بفرد ترانزیستورهای نانوشیت است. یک فرورفتگی در لایه های SiGe جا را برای یک spacer داخلی بین Sourceو drain باز می کند که در نهایت کنار ستون و فضایی که gate خواهد بود قرار داده می شود. این spacer عرض gate را مشخص می کند. سپس وقتی spacer های داخلی در جای خود قرار گرفتند، SiGe برداشته میشود. ALD (روش رسوب دادن لایه های اتمی)عایق و فلز gate را در فضای بین ورقات نانوی سیلیکونی قرار می دهد.

برای به حداقل رساندن اعوجاج و سایر عیب های شبکه، محتوای ژرمانیوم لایه های SiGe باید تا جای ممکن حداقل باشند. با این حال گزینندگی (selectivity) etch با محتوای Ge افزایش می یابد و فرسایش لایه های سیلیکونی در حین دندانه گذاری spacer یا رهاسازی کانال بر ضخامت کانال و در نتیجه آستانه ولتاژ تاثیر می گذارد.

نانو سیم های GAAترانزیستور (Nanowire GAA)

در آزمایشگاه چندین نهاد در حال کار بر روی نانو سیم ها برای gate-all-around FET هسند. برای مثال IBM اخیرا یک نانوسیم برای GAAFET سیلیکونی را معرفی کرده که به یک نانوسیم با مقیاس 30nm و یک گیت با مقیاس 60nm دست یافته است.این دستگاه دارای نانوسیم با مقیاس موثر 12.8 نانومتری بوده است.

برای ساخت GAA شرکت IBM دو مکان را بر روی یک زیرلایه(substrate) تعبیه کرده است که نانوسیم ها به صورت افقی و معلق بر روی این دومکان مورد نظرقرارداده شدند.سپس گیت های عمودی بالای این نانوسیم ها قرار گرفته اند.با این کار چندین گیت بالای یک مکان معلق مشترک تعبیه میشوند.

بر اساس گفته های IBM یک SPACER ساخته می شود سپس نانوسیم های سیلیکونی بیرون محوطه گیت بریده می شوند. سپس اپیتاکسی(یکی دیگر از روش های نشاندن اتم ها و تشکیل و رشد کریستال ها) سیلیکونیِ In-situ doped از مناطق ضربدری آشکار شده ی نانوسیم های سیلیکونی در لبه ی spacer ، رشد می کند. برای کامل کردن دستگاه از اتصالات مرسوم سیلیکاتی بر پایه نیکل و اتصالات داخلی(interconnects) مسی استفاده می شود.

نسخه های دیگری از gate-all-around نیز موجود است. برای مثال سویتک و لتی (Soitec and Leti)، دانشگاه ملی سنگاپور، اخیرا یک Ge gate-all-around nanowire PFET را معرفی کرده است. با عرض سیم 3.5 نانومتر، این دستگاه با یک ماده ی تغییر دهنده ی فاز به نام Ge2Sb2Te5 (GST)به عنوان یک تحریک کننده ی خطی ادغام شده بود که در نتیجه موبیلیته را بهبود بخشیده بود.

اضافه کنیم که دانشگاه ملی چنگ کونگ (Cheng Kung ) یک stacked silicon nanowire MOSFET ساخته است. MOSFET که می توان آن را به عنوان یک gate-all-around FET دسته بندی کرد همچنین از یک زیر لایه ی silicon-on-insulator (SOI) استفاده می کند. یک طرح ناخالص سازی انعطاف پذیر نیز طراحی شده است تا بتواند طراحی های با کارایی بالا و کم مصرف را با این فناوری انجام دهد.

محققان با استفاده از اپیتاکسی فوق شبکه ای سیلیکون / سیلیکون-ژرمانیم و یک فرآیند دوپینگ درجا (in-situ) برای سیم های انباشته شده ، یک FET (gate-all-around) چهار سیمه انباشته را ایجاد کرده اند. طول گیت برای دستگاه 10 نانومتر است. عرض کانال و ارتفاع هردو براساس طول مقیاس الکترواستاتیک 3.3 نانومتری 10 نانومتر هستند.

طبق یکی از مقالات این دانشگاه: “(دوپینگ) (طرح های) ولتاژ آستانه برای سیم های انباشته بسیار متفاوت از رویکرد معمول است ، به ویژه هنگامی که چندین لایه ترانزیستور بر روی یک لایه قرار دارند. دوپینگ نکردن کانال دارای مزیتی در موبیلیته است و انتظار می رود مسئله نوسان تصادفی را کاهش دهد ، اما نیاز به استفاده از طرح multi-Vt که معمولاً در برنامه های SoC استفاده می شود را برآورده نمی کند در عوض ، عملکردهای مختلف گیت ها (یا مواد گیت ها) برای Vt های مختلف مورد نیاز خواهد بود ، و از این رو ، چنین رویکرد بدون جابجایی پیچیده تر خواهد بود.”

محققان رویکرد متفاوتی را اعمال کرده اند. براساس گفته ی آن ها “در طی فرایند اپیتاکسی ، کانال دوپینگ شده درجا (in-situ doped) برای هر یک از سیمهای انباشته شده اجرا می شود. MOSFET های انباشته شده-دوپ شده گزینه های انعطاف پذیر برای تنظیم Vt را ارائه می دهند.”